Memory Performance:

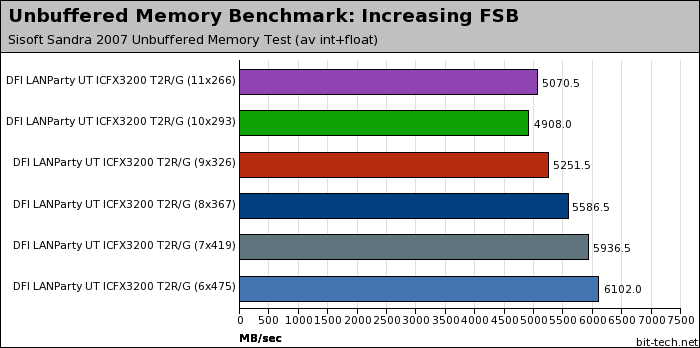

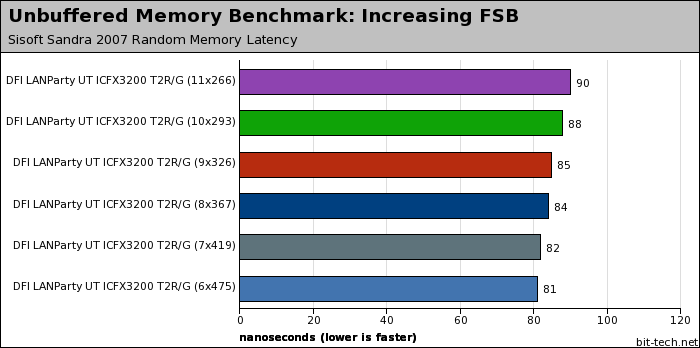

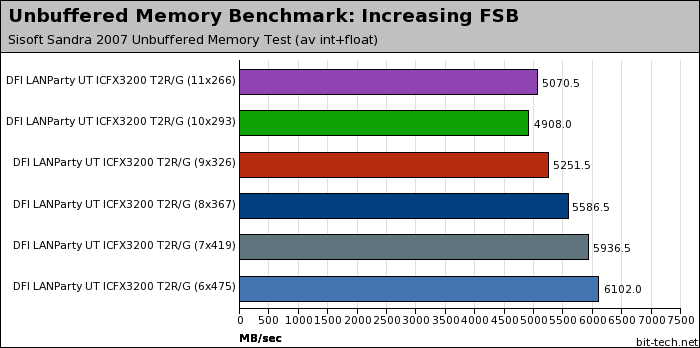

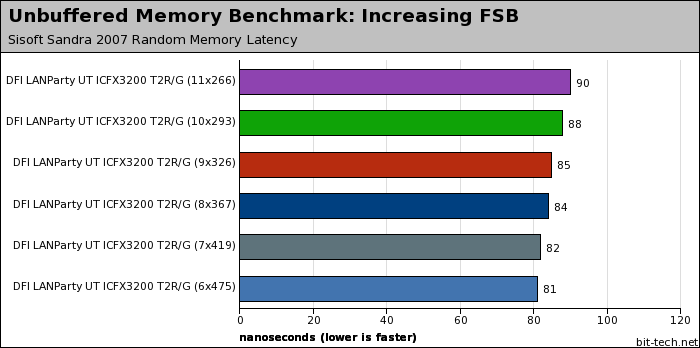

We tested the ICFX3200-T2R/G board, progressively overclocking the CPU front side bus (FSB) and keeping the CPU as close to the original stock speed of 2933MHz as possible. We found an upper limit of 475MHz which was below the 489MHz needed to keep it at 2933MHz, but we still see an increase in usable memory bandwidth. The initial drop is due to the CPU FSB strap changes internally within the RD600 chipset. This setting was left on Auto, and the maximum strap is 333. The latency also linearly decreases as we increase the CPU FSB, despite the fact we are keeping the memory at a constant speed.

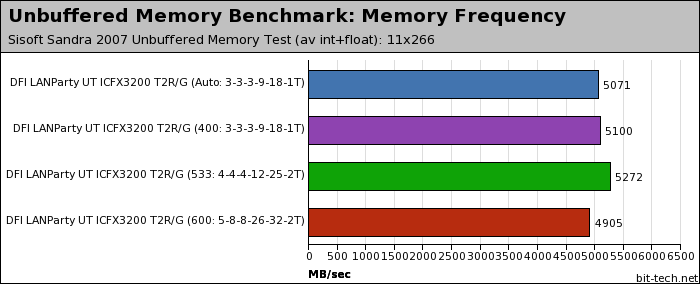

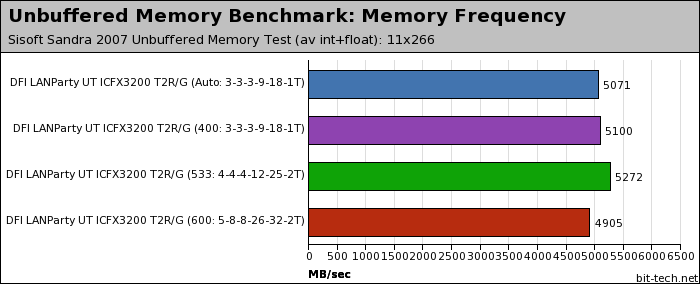

Comparing the raw memory bandwidth scores, leaving our X6800 CPU at a stock 2933MHz, we can see that for a 25% increase in clock speed there is only a 3.9% increase in maximum theoretical bandwidth, but increasing this to 33% clock speed we see a

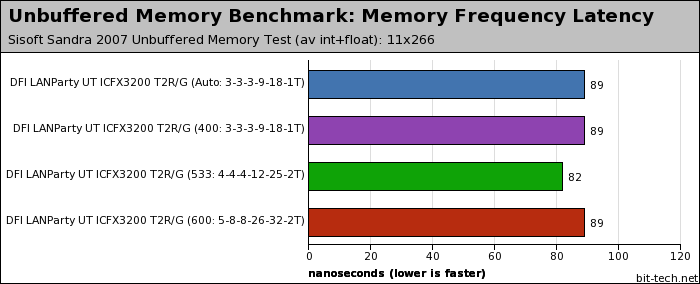

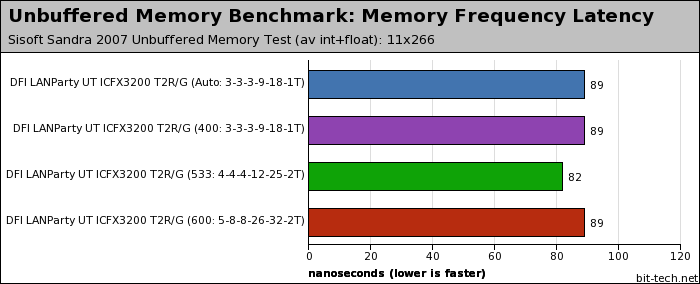

drop in overall bandwidth. The offset of increasing the speed of the memory is that the timings need to become more relaxed, and despite using PC8500 and PC9136 memory we had to drop the timings from 3-3-3-9-18-1T at 400MHz (800MHz DDR2) memory bus to 4-4-4-12-25-2T at 533MHz (1066MHz DDR2) and then finally 5-8-8-26-32-2T at 600MHz (1200MHz DDR2).

We

previously showed the effect of memory timings at stock PC6400 (DDR2 800) using a 975X board.

Want to comment? Please log in.